高級模擬集成電路設(shè)計 從原理到實踐

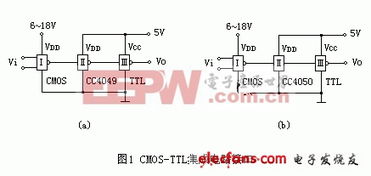

高級模擬集成電路設(shè)計是電子工程領(lǐng)域中極具挑戰(zhàn)性和創(chuàng)新性的分支,它專注于在單芯片上集成復(fù)雜的模擬功能,以滿足現(xiàn)代電子系統(tǒng)對高性能、低功耗和微型化的需求。與數(shù)字集成電路不同,模擬電路處理的信號是連續(xù)的電壓或電流,其設(shè)計更側(cè)重于對噪聲、線性度、帶寬、功耗和工藝偏差等關(guān)鍵性能指標的精確控制和優(yōu)化。

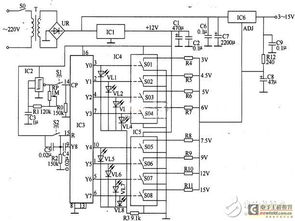

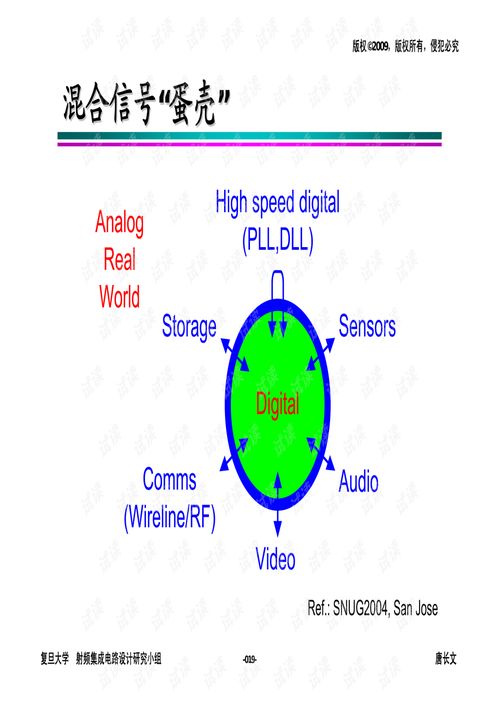

高級模擬集成電路的核心設(shè)計范疇包括但不限于:高精度運算放大器、數(shù)據(jù)轉(zhuǎn)換器(ADC/DAC)、鎖相環(huán)(PLL)、低壓差線性穩(wěn)壓器(LDO)、射頻前端電路以及電源管理芯片等。這些電路是通信系統(tǒng)、傳感器接口、醫(yī)療設(shè)備、汽車電子和消費類產(chǎn)品的基石。

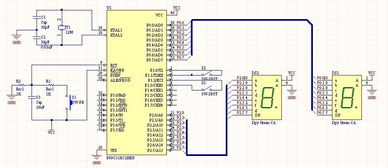

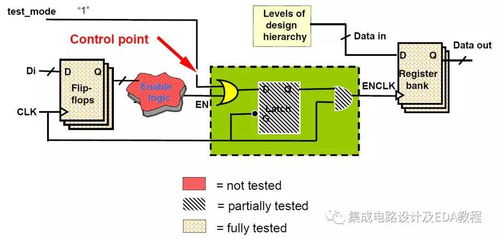

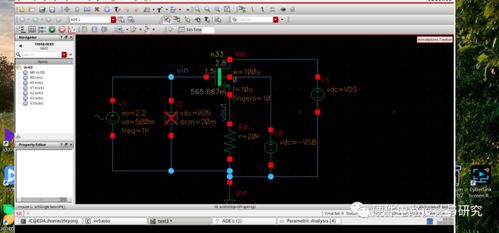

設(shè)計過程通常始于系統(tǒng)級規(guī)劃,明確性能指標和工藝選擇。隨后進入晶體管級設(shè)計,工程師需要深入理解半導(dǎo)體器件的物理特性,利用小信號模型、噪聲分析和穩(wěn)定性判據(jù)(如奈奎斯特準則)來構(gòu)建和優(yōu)化電路。版圖設(shè)計是模擬IC設(shè)計中至關(guān)重要的一環(huán),需要精心布局布線以最小化寄生效應(yīng)、匹配誤差和襯底噪聲耦合,同時確保可靠的可制造性。

隨著工藝節(jié)點不斷演進至納米尺度,設(shè)計面臨新的挑戰(zhàn)。短溝道效應(yīng)、工藝波動增大以及電源電壓降低,使得傳統(tǒng)設(shè)計方法面臨瓶頸。因此,現(xiàn)代高級模擬設(shè)計廣泛采用先進技術(shù),如自適應(yīng)偏置、校準技術(shù)、數(shù)字輔助模擬電路以及基于機器學習的設(shè)計自動化工具,以在受限的設(shè)計空間中實現(xiàn)最優(yōu)性能。

高級模擬集成電路設(shè)計是一門融合了深厚理論基礎(chǔ)、豐富實踐經(jīng)驗和創(chuàng)造性問題解決能力的學科。它不僅是技術(shù)的前沿,更是推動整個電子信息產(chǎn)業(yè)持續(xù)創(chuàng)新的核心驅(qū)動力。掌握其精髓,意味著能夠?qū)⒊橄蟮碾姎馓匦赞D(zhuǎn)化為穩(wěn)定、高效且經(jīng)濟的硅上現(xiàn)實,為智能世界的構(gòu)建奠定堅實的硬件基礎(chǔ)。

如若轉(zhuǎn)載,請注明出處:http://www.35zn.cn/product/69.html

更新時間:2026-03-09 14:19:57